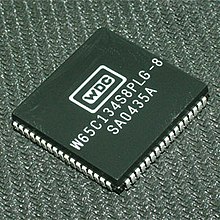

The Western Design Center (WDC) W65C134S is an 8-bit CMOS microcontroller based on a W65C02S processor core, which is a superset of the MOS Technology 6502 processor.

The W65C134S consists of a fully static 8-bit W65C02S CPU core, 4 KB of ROM containing a machine language monitor, 192 bytes of SRAM, two 16 bit timers, one 16-bit Watch-Dog Timer (WDT) with "restart" interrupt, one UART with baud rate timer, a low power Serial Interface Bus (SIB) configured as a token passing local area network, twenty-two priority encoded interrupts, two crystal inputs (slow 32.768KHz and fast up to 8-MHz), Bus Control Register (BCR) for external memory bus control, interface circuitry for peripheral devices, and many low power features. The W65C134S has been developed for high-reliability applications, as well as where minimum power is required.